US 20070242016A1

(19) United States

(12) Patent Application Publication

Choi(10) Pub. No.: US 2007/0242016 A1

(43) Pub. Date: Oct. 18, 2007(54) PIXEL, ORGANIC LIGHT EMITTING

DISPLAY DEVICE, AND DRIVING METHOD

THEREOF

## Publication Classification

(51) Int. Cl.

*G09G 3/36* (2006.01)

(52) U.S. Cl. ..... 345/92

(57)

(76) Inventor: Sang Moo Choi, Suwon-si (KR)

## ABSTRACT

Correspondence Address:

CHRISTIE, PARKER & HALE, LLP

PO BOX 7068

PASADENA, CA 91109-7068

(21) Appl. No.: 11/655,400

(22) Filed: Jan. 19, 2007

## (30) Foreign Application Priority Data

Apr. 17, 2006 (KR) ..... 10-2006-0034616

A method for driving an organic light emitting display device capable of reducing the number of output lines in a data driver, as well as ensuring a sufficient driving time. The method for driving the organic light emitting display device includes steps of supplying a data signal and a reset voltage to an output line during a horizontal period; supplying the data signal and the reset voltage, supplied to the output line, to a plurality of data lines using a demultiplexer; charging a voltage corresponding to the data signal in a pixel connected with one of the data lines during a period when a scan signal is supplied to a current scan line of the pixel; and allowing the pixel to emit light corresponding to the charged voltage.

FIG. 1

(PRIOR ART)

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

**PIXEL, ORGANIC LIGHT EMITTING

DISPLAY DEVICE, AND DRIVING METHOD

THEREOF**

CROSS-REFERENCE TO RELATED

APPLICATION

[0001] This application claims priority to and the benefit of Korean Patent Application No. 10-2006-0034616, filed on Apr. 17, 2006, in the Korean Intellectual Property Office, the entire content of which is incorporated herein by reference.

BACKGROUND

[0002] 1. Field of the Invention

[0003] The present invention relates to an organic light emitting display and a driving method thereof, and more specifically, to a pixel of an organic light emitting display device and a driving method thereof.

[0004] 2. Discussion of Related Art

[0005] An organic light emitting display device is a flat panel display device that displays an image using an organic light emitting diode which generates lights by recombination of electrons and holes. Such an organic light emitting display device has a rapid response time and may be driven with a low power consumption. A conventional organic light emitting display device allows an organic light emitting diode to emit lights by supplying an electric current, corresponding to data signals, to the organic light emitting diode using a drive transistor formed in every pixel.

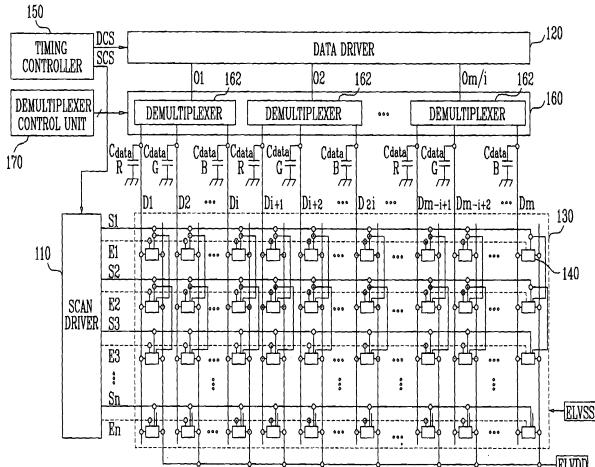

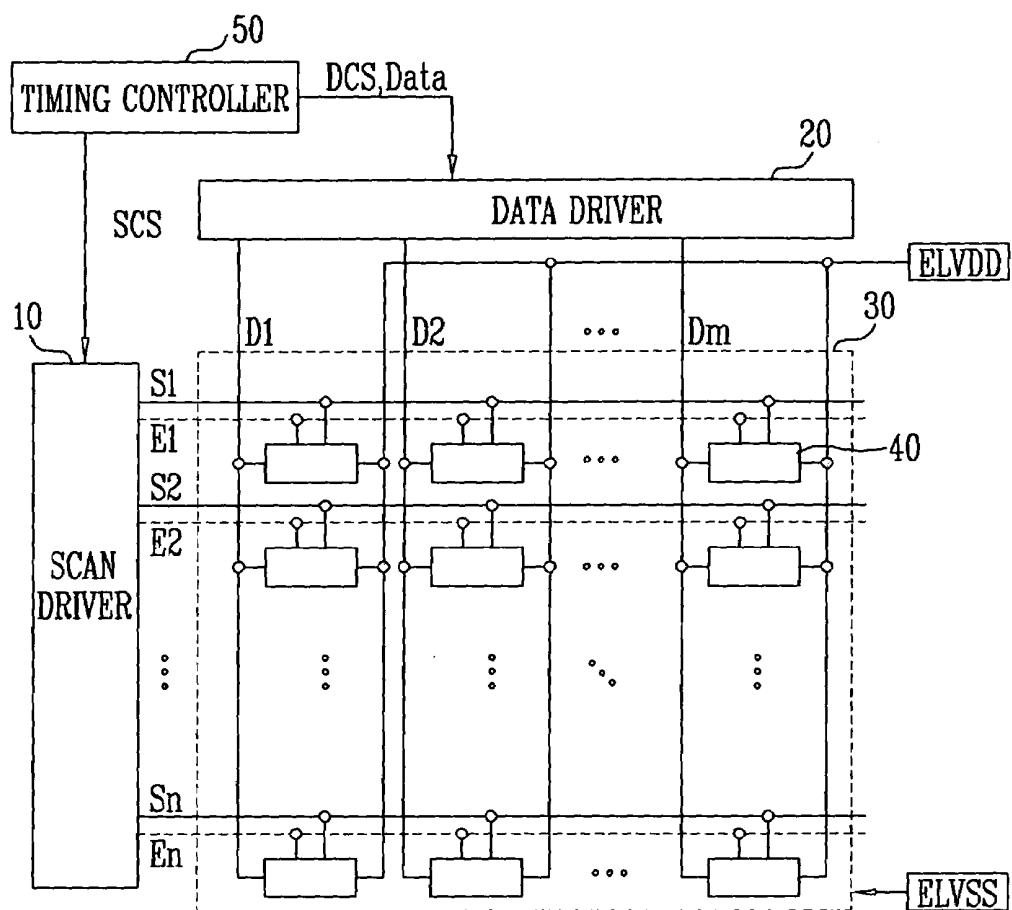

[0006] FIG. 1 is a schematic view showing a conventional organic light emitting display device.

[0007] Referring to FIG. 1, the conventional organic light emitting display device includes a pixel unit (or display region) 30 including pixels 40 formed at cross regions of scan lines (S1 to Sn) and data lines (D1 to Dm); a scan driver 10 for driving the scan lines (S1 to Sn) and emission control lines (E1 to En); a data driver 20 for driving the data lines (D1 to Dm); and a timing controller 50 for controlling the scan driver 10 and the data driver 20.

[0008] The scan driver 10 generates scan signals in response to scan driving control signals (SCS) supplied from the timing controller 50, and sequentially supplies the generated scan signals to the scan lines (S1 to Sn). Also, the scan driver 10 generates emission control signals in response to the scan driving control signals (SCS), and sequentially supplies the generated emission control signals to the emission control lines (E1 to En).

[0009] The data driver 20 generates data signals in response to the data driving control signals (DCS) supplied from the timing controller 50, and supplies the generated data signals to the data lines (D1 to Dm). Here, the data driver 20 supplies data signals, corresponding to one line, to the data lines (D1 to Dm) during every horizontal period (1H).

[0010] The timing controller 50 generates data driving control signals (DCS) and scan driving control signals (SCS) to correspond to synchronizing signals supplied from an external source. The data driving control signals (DCS) generated in the timing controller 50 are supplied to the data driver 20, and the scan driving control signals (SCS) are supplied to the scan driver 10. Also, the timing controller 50 rearranges data supplied from an external source, and then supplies the rearranged data to the data driver 20.

[0011] The pixel unit (or display region) 30 receives a first power of a first power supply (ELVDD) and a second power of a second power supply (ELVSS) externally, and supplies the first power of the first power supply (ELVDD) and the second power of the second power supply (ELVSS) to each of the pixels 40. The pixels 40 receiving the first power of the first power supply (ELVDD) and the second power of the second power supply (ELVSS) control a current capacity to correspond to the data signals (i.e., the current capacity that flows from the first power supply (ELVDD) to the second power supply (ELVSS) via the organic light emitting diode (OLED)). In this case, an emission time of the pixels 40 is controlled to correspond to the emission control signals.

[0012] In the conventional organic light emitting display device driven in the manner as described above, the pixels 40 are arranged at crossings of the scan lines (S1 to Sn) and the data lines (D1 to Dm). Here, the data driver 20 includes the number m of output lines so that the data driver 20 can supply the data signals to the number m of the data lines (D1 to Dm), respectively. That is, the data driver 20 includes the same number of the output lines as that of the data lines (D1 to Dm) in the conventional organic light emitting display device. For this purpose, the data driver 20 includes a relatively large number of data driving circuits to drive the output lines, and therefore the manufacturing cost is increased. In particular, as resolution and size of the pixel unit 30 increase, the number of the output lines of the data driver 20 also increases to thereby increase the manufacturing cost of the pixel unit 30.

SUMMARY OF THE INVENTION

[0013] Accordingly, an aspect of the present invention provides a pixel capable of reducing the number of output lines in a data driver while ensuring a sufficient driving time, an organic light emitting display device using the same, and a driving method thereof.

[0014] A first embodiment of the present invention provides a method for driving an organic light emitting display device, including steps of supplying a data signal and a reset voltage to an output line during a horizontal period; supplying the data signal and the reset voltage, supplied to the output line, to a plurality of data lines using a demultiplexer; charging a voltage corresponding to the data signal in a pixel connected with one of the data lines during a period when a scan signal is supplied to a current scan line of the pixel; and allowing the pixel to emit light corresponding to the charged voltage.

[0015] A second embodiment of the present invention provides an organic light emitting display device including a data driver for supplying a data signal and a reset voltage to an output line during every horizontal period; a demultiplexer coupled to the output line to supply the data signal and the reset voltage to a plurality of data lines; a scan driver for supplying a scan signal during every horizontal period; and a pixel connected with one of the data lines, a previous scan line, and a current scan line, wherein the pixel is reset by the reset voltage during a period when the scan signal is supplied to the previous scan line, and is charged with a voltage corresponding to the data signal when the scan signal is supplied to the current scan line.

[0016] A third embodiment of the present invention provides a pixel including an organic light emitting diode; a storage capacitor for charging a voltage corresponding to a data signal supplied to one of a plurality of data lines; a first

transistor for supplying an electric current, corresponding to a voltage charged in the storage capacitor, to the organic light emitting diode; a second transistor connected to the one of the data lines, a current scan line, and a second electrode of the first transistor, the second transistor being adapted to turn on when a scan signal is supplied to the current scan line; a third transistor connected between a first electrode and a gate electrode of the first transistor and being adapted to turn on when the scan signal is supplied to the current scan line; and a fourth transistor connected between the gate electrode of the first transistor and the one of the data line and being adapted to turn on when the scan signal is supplied to a previous scan line.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0017] The accompanying drawings, together with the specification, illustrate exemplary embodiments of the present invention, and, together with the description, serve to explain the principles of the present invention.

[0018] FIG. 1 is a schematic view showing a conventional organic light emitting display device.

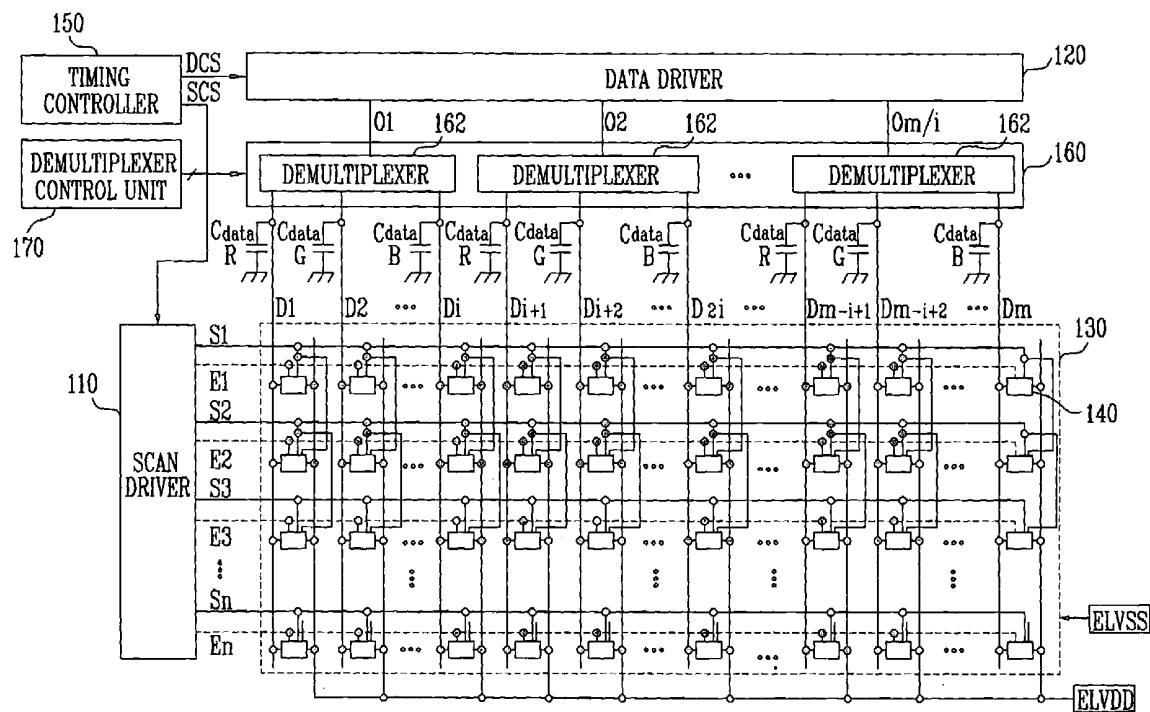

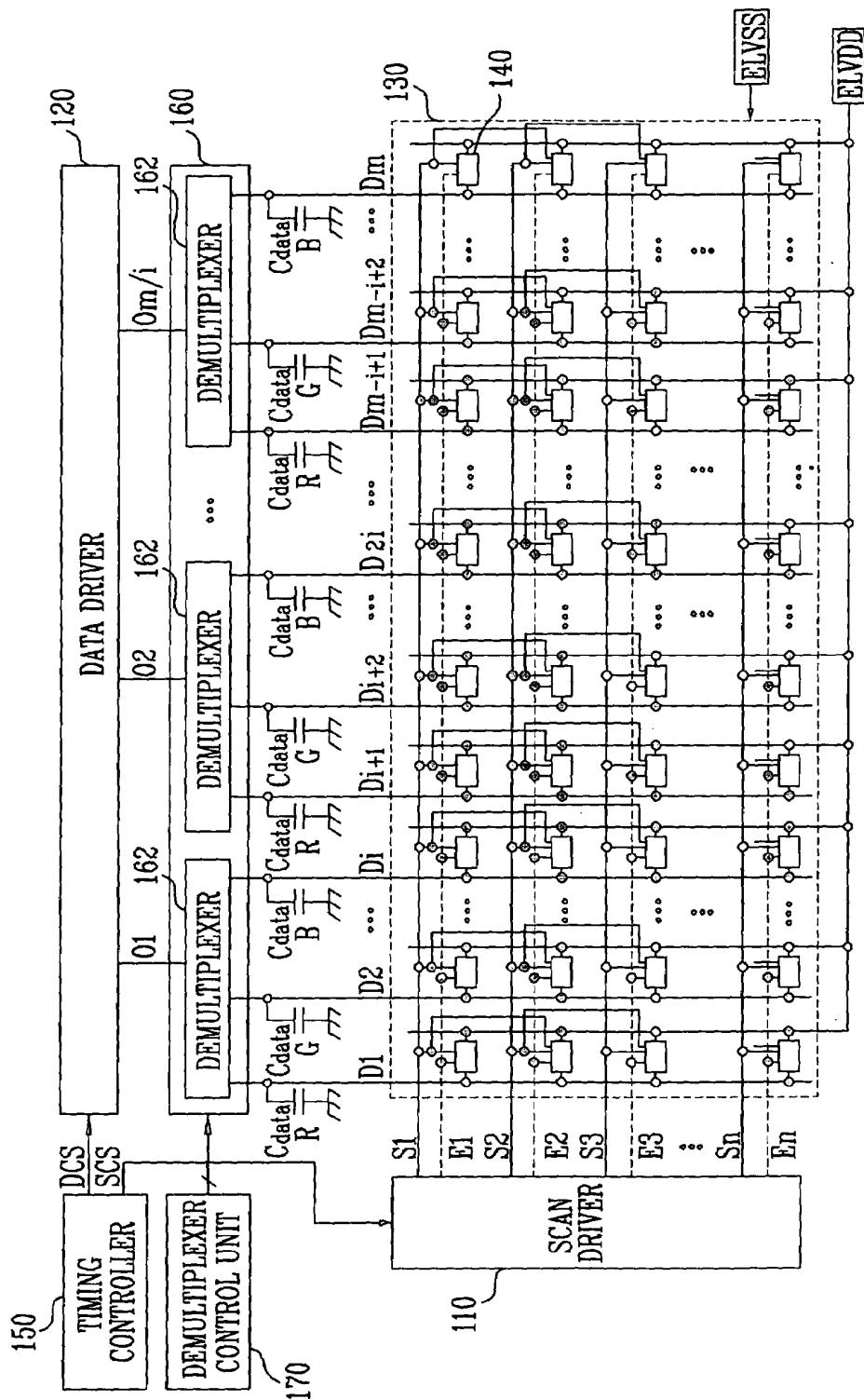

[0019] FIG. 2 is a schematic view showing an organic light emitting display device according to one embodiment of the present invention.

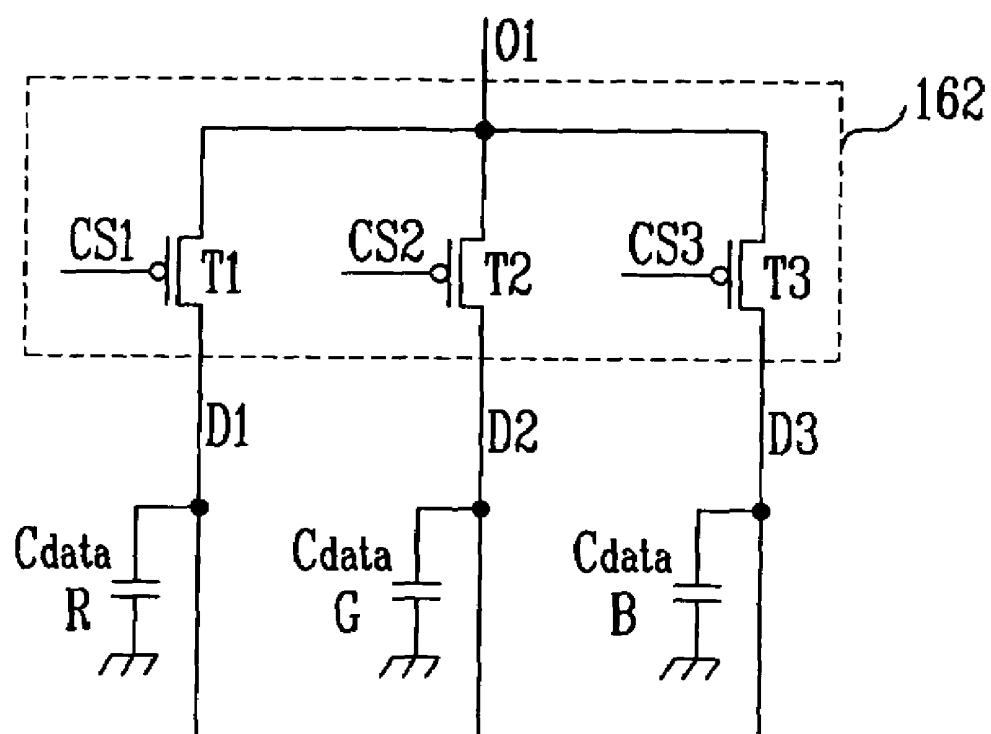

[0020] FIG. 3 is a circuit view showing a demultiplexer as shown in FIG. 2.

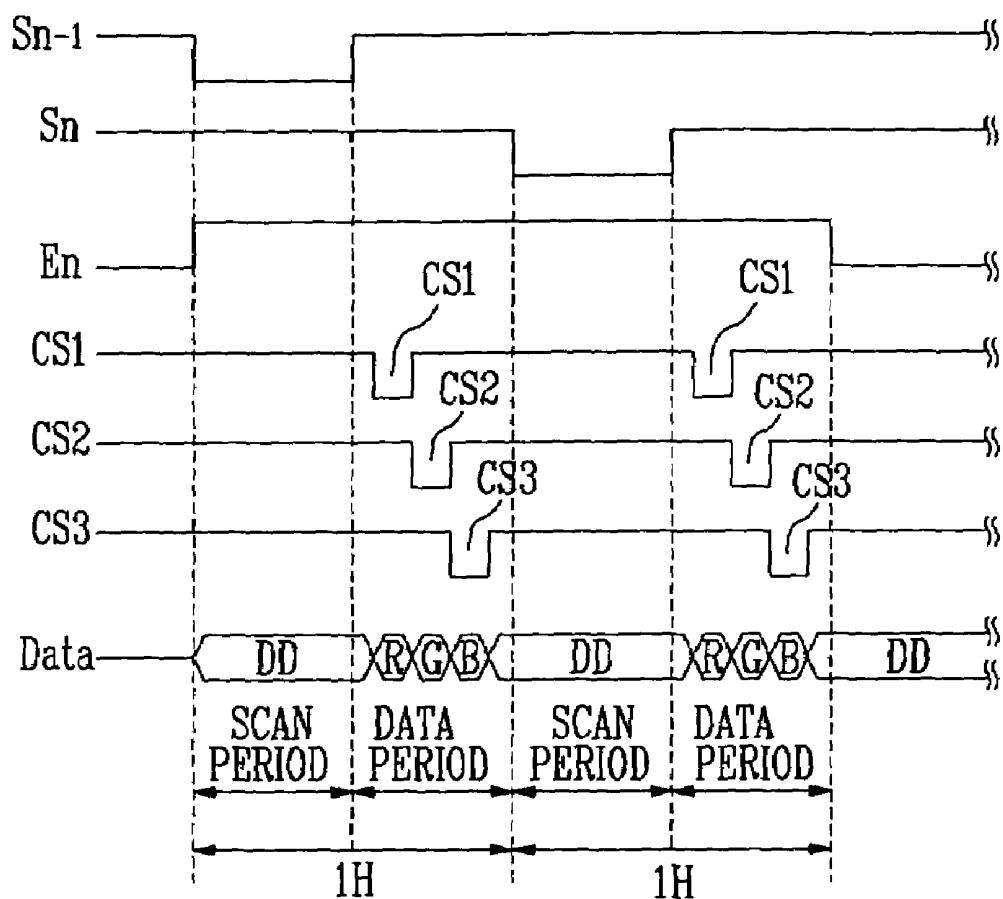

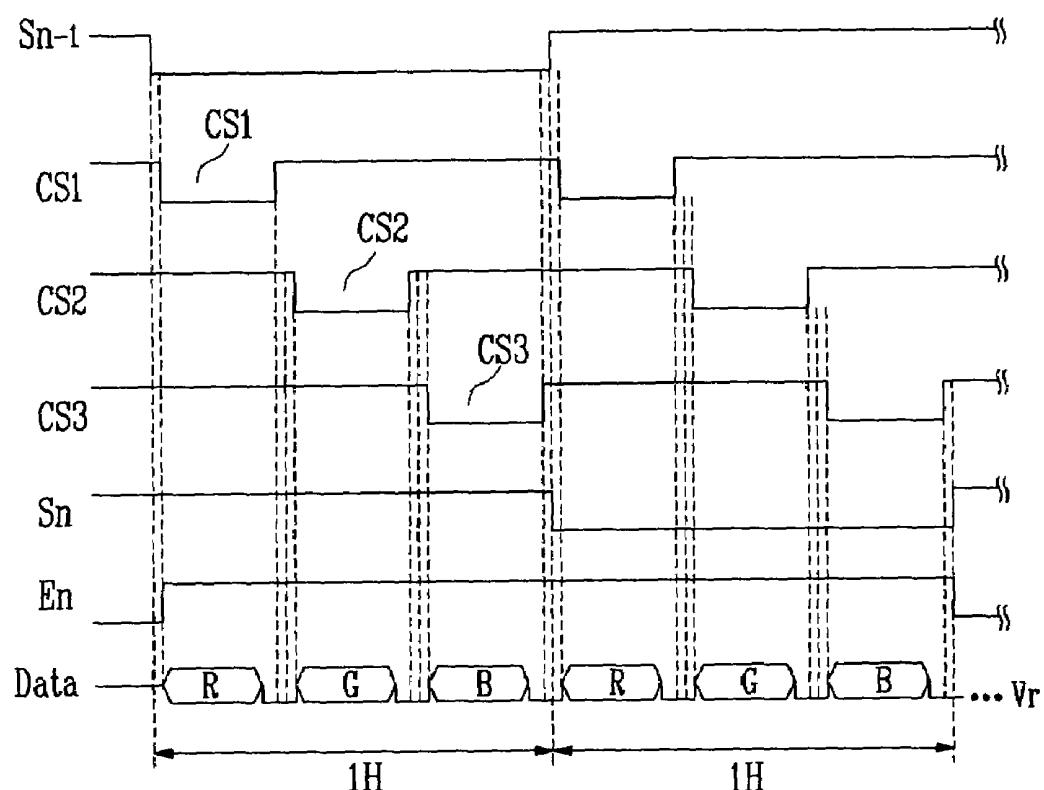

[0021] FIG. 4 is a waveform view showing a method for driving an organic light emitting display device according to a first embodiment of the present invention.

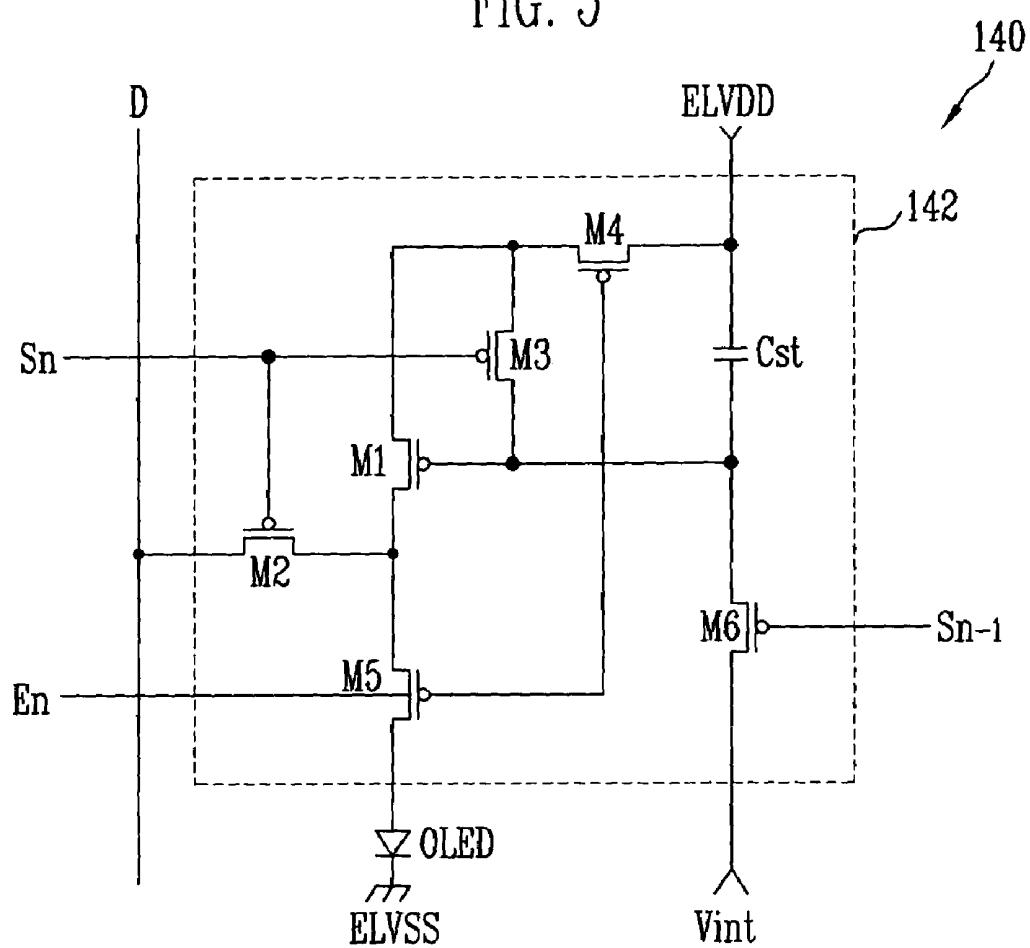

[0022] FIG. 5 is a circuit view showing a pixel adapted to be driven by the method according to the first embodiment.

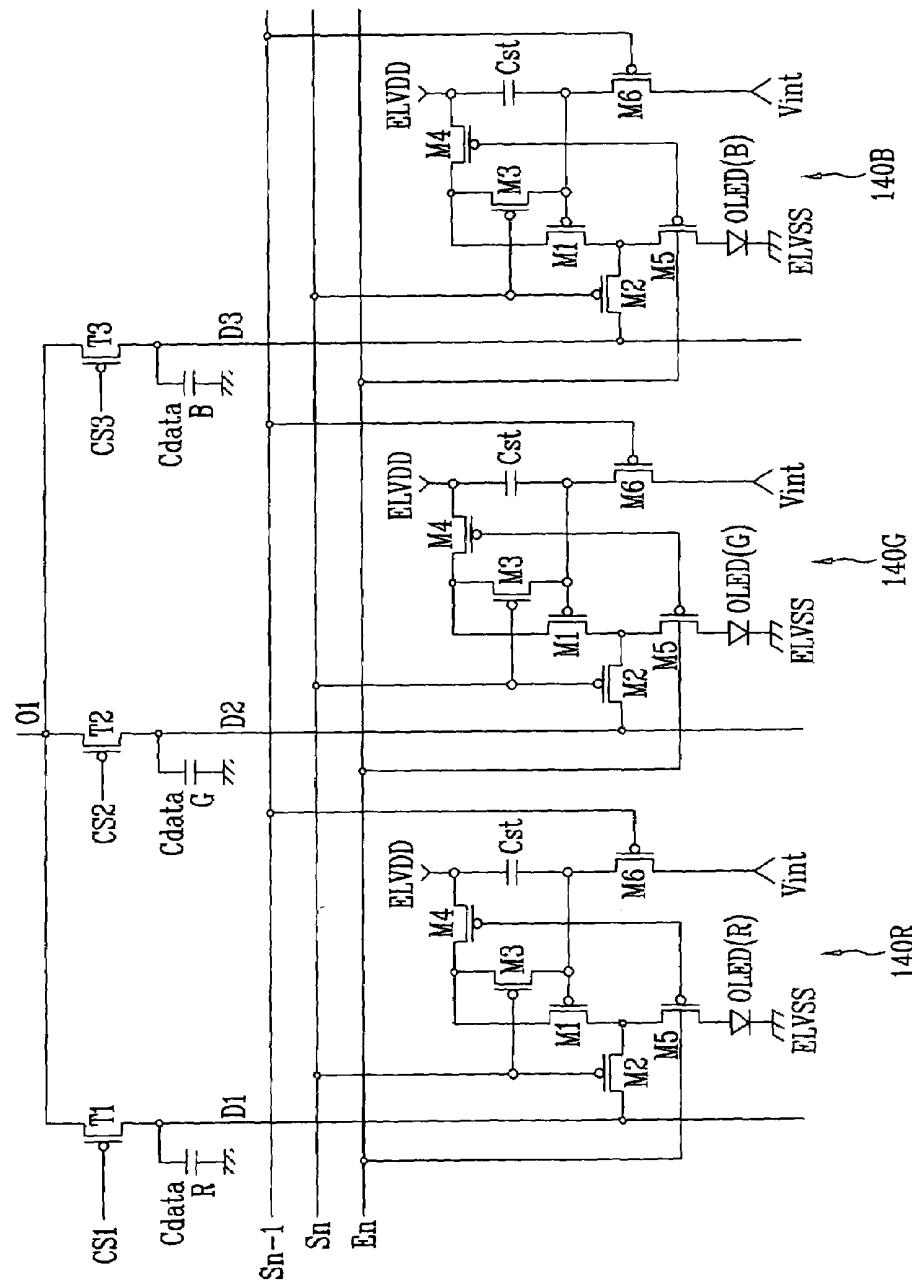

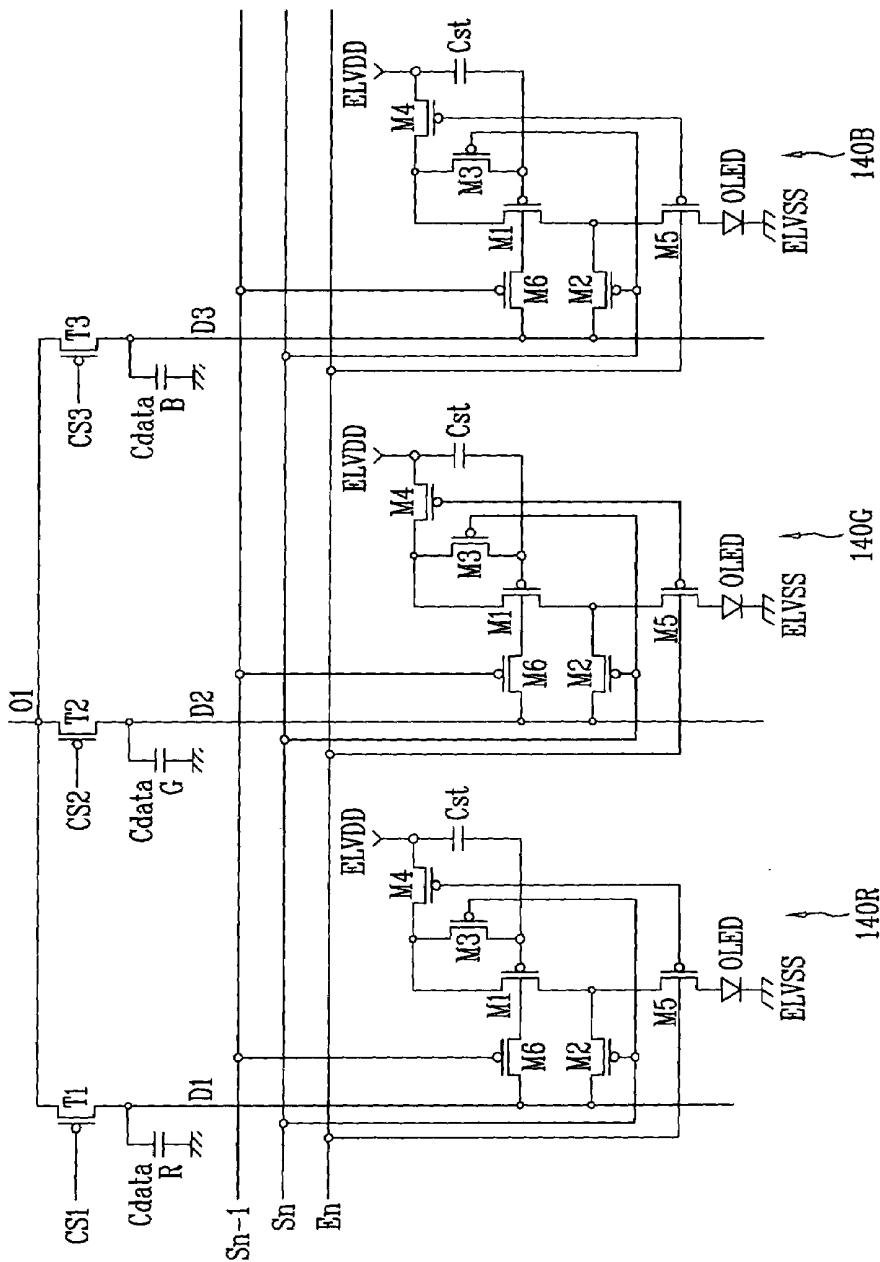

[0023] FIG. 6 is a cross-sectional view showing a configuration in which the demultiplexer is combined with the pixel as shown in FIG. 5.

[0024] FIG. 7 is a waveform view showing a method for driving an organic light emitting display device according to a second embodiment of the present invention.

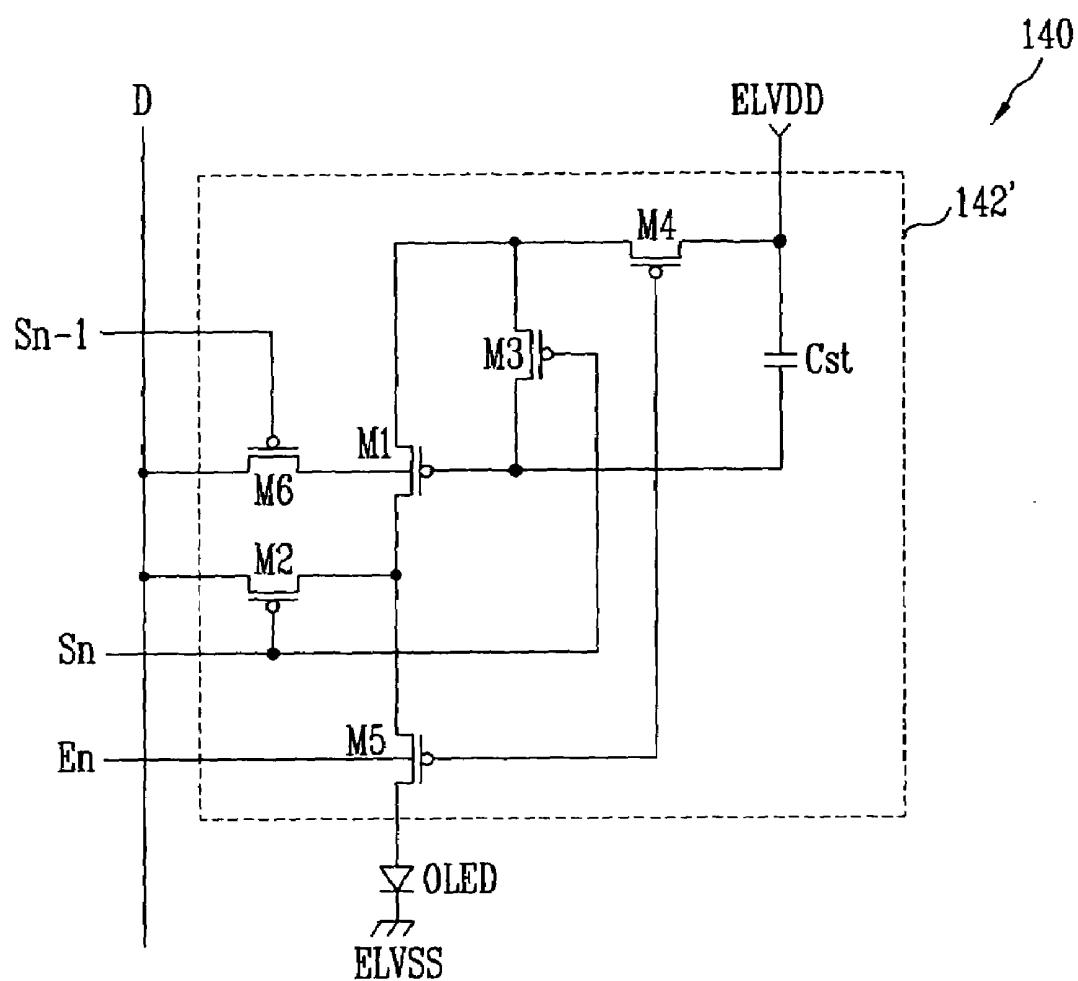

[0025] FIG. 8 is a circuit view showing a pixel adapted to be driven by the method according to the second embodiment.

[0026] FIG. 9 is a cross-sectional view showing a configuration in which the demultiplexer is combined with the pixel as shown in FIG. 8.

#### DETAILED DESCRIPTION

[0027] In the following detailed description, only certain exemplary embodiments of the present invention are shown and described, by way of illustration. As those skilled in the art would recognize, the invention may be embodied in many different forms and should not be construed as being limited to the embodiments set forth herein. Like reference numerals designate like elements throughout the specification.

[0028] FIG. 2 is a schematic view showing an organic light emitting display device according to one embodiment of the present invention.

[0029] Referring to FIG. 2, the organic light emitting display device includes a scan driver 110, a data driver 120, a pixel unit (or display region) 130, a timing controller 150, a demultiplexer block unit 160, a demultiplexer control unit 170, and data capacitors (Cdata).

[0030] The pixel unit (or display region) 130 includes a plurality of pixels 140 arranged in a region defined by the

scan lines (S1 to Sn) and the data lines (D1 to Dm). Each of the pixels 140 is allowed to emit lights having a luminance (e.g., a predetermined luminance) corresponding to data signals supplied from the data lines (D). For this purpose, each of the pixels 140 is connected to two scan lines, one data line, a power line (not shown) for supplying a first power of a first power supply (ELVDD), and a reset power line (not shown) for supplying a reset power of a reset power supply. For example, each of the pixels 140 positioned in the last horizontal line is connected to an n-1<sup>st</sup> scan line (Sn-1), an n<sup>th</sup> scan line (Sn), a data line (D), a power line, and a reset power line. Also, the pixel unit further includes a scan line (for example, a 0<sup>th</sup> scan line (S0)) so that the 0<sup>th</sup> scan line can be connected to the pixels 140 positioned in the first horizontal line.

[0031] The scan driver 110 generates scan signals in response to the scan driving control signal (SCS) supplied from the timing controller 150, and sequentially supplies the generated scan signals to the scan lines (S1 to Sn). Here, the scan driver 110 supplies the scan signals during a portion of the first horizontal period (1H), as shown in FIG. 4.

[0032] In more detail, one horizontal period (1H) is divided into a scan period and a data period in a first embodiment of the present invention. The scan driver 110 supplies scan signals to the scan line (S) during the scan period of the one horizontal period (1H). However, the scan driver 110 does not supply scan signals to the scan line (S) during the data period of the one horizontal period (1H). In addition, the scan driver 110 generates emission control signals in response to the scan driving control signals (SCS), and sequentially supplies the generated emission control signals to the emission control lines (E1 to En). Here, the emission control signals are supplied during at least two horizontal periods.

[0033] The data driver 120 generates data signals in response to the data driving control signal (DCS) supplied from the timing controller 150, and supplies the generated data signals to the output lines (O1 to Om/i). Here, the data driver 120 sequentially supplies at least the number i ("i" represents an integer greater than 2) of the data signals to each of the output lines (O1 to Om/i) during the one horizontal period (1H), as shown in FIG. 4.

[0034] In more detail, the data driver 120 sequentially supplies the number i of data signals (R,G,B), which are later supplied to actual pixels, during the data period of the one horizontal period (1H). Here, supply periods of the data signals (R,G,B) and the scan signals, which are later supplied to the pixels, are not overlapped with each other since the data signals (R,G,B) which are later supplied to the pixels are supplied only during the data period. Also, in one embodiment, the data driver 120 supplies a dummy data (DD), which does not contribute to luminance, during the scan period of the one horizontal period (1H). Here, in another embodiment, the dummy data (DD) is not supplied since it does not contributes to luminance.

[0035] The timing controller 150 generates data driving control signals (DCS) and scan driving control signals (SCS) to correspond to synchronizing signals supplied from an external source. The data driving control signals (DCS) generated in the timing controller 150 are supplied to the data driver 120, and the scan driving control signals (SCS) are supplied to the scan driver 110.

[0036] The demultiplexer block unit 160 includes the number m/i of demultiplexers 162. That is, the demulti-

plexer block unit **160** has the same number of the demultiplexers **162** as that of the output lines ( $O_1$  to  $O_{m/i}$ ), and each of the demultiplexers **162** is connected to one of the output lines ( $O_1$  to  $O_{m/i}$ ). Also, each of the demultiplexers **162** is connected to the number  $i$  of the data lines ( $D$ ). Such a demultiplexer **162** supplies the number  $i$  of data signals, supplied to the output lines ( $O$ ), to the number  $i$  of the data lines ( $D$ ) during the data period.

[0037] As described above, the number of the output lines ( $O$ ) included in the data driver **120** can thus be reduced if the data signals supplied to the one output line ( $O$ ) are supplied to the number  $i$  of the data lines ( $D$ ). For example, if the number  $i$  is set to **3**, then the number of the output lines ( $O$ ) included in the data driver **120** is reduced to a third of the number in the device of FIG. 1, and therefore the number of data driving circuits included in the data driver **120** is also reduced. That is, the manufacturing cost may be lowered in an embodiment of the present invention by supplying the data signals, supplied to the one output line ( $O$ ), to the number  $i$  of the data lines ( $D$ ) using the demultiplexer **162**.

[0038] The demultiplexer control unit **170** supplies the number  $i$  of control signals to each of the demultiplexers **162** during the data period of the one horizontal period (**1H**) so that the number  $i$  of the data signals supplied to the output lines ( $O$ ) are divided into and supplied to the number  $i$  of the data lines ( $D$ ). Here, the demultiplexer control unit **170** sequentially supplies the number  $i$  of the control signals to prevent the number  $i$  of the control signals, supplied during the data period, from being overlapped with each other, as shown in FIG. 4. Also, FIG. 2 shows that the demultiplexer control unit **170** is installed in the outside of the timing controller **150**, but the present invention is not limited thereto. For example, the demultiplexer control unit **170** may be installed in the inside of the timing controller **150**.

[0039] The data capacitors ( $C_{data}$ ) are disposed in every data line ( $D$ ). Such a data capacitor ( $C_{data}$ ) temporarily stores the data signals supplied to the data lines ( $D$ ), and supplies the stored data signals to the pixels **140**. Here, the data capacitors ( $C_{data}$ ) use a parasitic capacitor that is equivalently formed in (or on) the data lines ( $D$ ). Here, the parasitic capacitor equivalently formed in (or on) the data lines ( $D$ ) may stably store the data signals since the parasitic capacitor has a larger capacitance than that of a storage capacitor formed in each of the pixels **140**.

[0040] FIG. 3 is a circuit view of a demultiplexer as shown in FIG. 2. For convenience of description, it is assumed that the number  $i$  is set to **3** in FIG. 3. In addition, the demultiplexer **162** connected to the first output line ( $O_1$ ) is shown in FIG. 3.

[0041] Referring to FIG. 3, each of the demultiplexers **162** includes a first switching element (**T1**), a second switching element (**T2**), and a third switching element (**T3**).

[0042] The first switching element (**T1**) is connected between the first output line ( $O_1$ ) and the first data line ( $D_1$ ). Such a first switching element (**T1**) is turned on when the first control signal ( $CS_1$ ) is supplied from the demultiplexer control unit **170**, to thereby supply the data signals, supplied to the first output line ( $O_1$ ), to the first data line ( $D_1$ ). The data signals supplied to the first data line ( $D_1$ ) are temporarily stored in the first data capacitor ( $C_{dataR}$ ) when the first control signal ( $CS_1$ ) is supplied from the demultiplexer control unit **170**.

[0043] The second switching element (**T2**) is connected between the first output line ( $O_1$ ) and the second data line

( $D_2$ ). Such a second switching element (**T2**) is turned on when the second control signal ( $CS_2$ ) is supplied from the demultiplexer control unit **170**, to thereby supply the data signals, supplied to the first output line ( $O_1$ ), to the second data line ( $D_2$ ). The data signals supplied to the second data line ( $D_2$ ) are temporarily stored in the second data capacitor ( $C_{dataG}$ ) when the second control signal ( $CS_2$ ) is supplied from the demultiplexer control unit **170**.

[0044] The third switching element (**T3**) is connected between the first output line ( $O_1$ ) and the third data line ( $D_3$ ). Such a third switching element (**T3**) is turned on when the third control signal ( $CS_3$ ) is supplied from the demultiplexer control unit **170**, to thereby supply the data signals, supplied to the first output line ( $O_1$ ), to the third data line ( $D_3$ ). The data signals supplied to the third data line ( $D_3$ ) are temporarily stored in the third data capacitor ( $C_{dataB}$ ) when the third control signal ( $CS_3$ ) is supplied from the demultiplexer control unit **170**.

[0045] FIG. 5 is a circuit view showing a configuration of a pixel adapted to be driven by a method according to a first embodiment of the present invention. The configuration of the pixel as shown in FIG. 5 is one example of the present invention, but the present invention is not limited thereto.

[0046] Referring to FIG. 5, each of the pixels **140** of the present embodiment includes an organic light emitting diode (OLED); and a pixel circuit **142** connected to the data line ( $D$ ), the scan line ( $S_n$ ), and the emission control line ( $E_n$ ) to control the organic light emitting diode (OLED).

[0047] An anode electrode of the organic light emitting diode (OLED) is connected to the pixel circuit **142**, and a cathode electrode is connected to a second power supply (ELVSS). The second power supply (ELVSS) is set to a lower voltage, for example, ground voltage, than that of the first power supply (ELVDD). The organic light emitting diode (OLED) generates light of red, green or blue color to correspond to a current capacity supplied from the pixel circuit **142**.

[0048] The pixel circuit **142** includes a storage capacitor ( $C_{st}$ ) and a sixth transistor (**M6**) connected between the first power supply (ELVDD) and the reset power supply ( $V_{int}$ ); a fourth transistor (**M4**), a first transistor (**M1**), and a fifth transistor (**M5**) connected between the first power supply (ELVDD) and the organic light emitting diode (OLED); a third transistor (**M3**) connected between the gate electrode and the first electrode of the first transistor (**M1**); and a second transistor (**M2**) connected between the data line ( $D$ ) and the second electrode of the first transistor (**M1**).

[0049] Here, the first electrode is set to be a drain electrode or a source electrode, and the second electrode is set to be the other one of the source and drain electrodes. For example, if the first electrode is set to be the source electrode, then the second electrode is set to be the drain electrode. Also, the first to sixth transistors (**M1** to **M6**) are shown as P-type MOSFETs in FIG. 5, but the present invention is not limited thereto. However, polarity of a driving waveform is reversed if the first to sixth transistors (**M1** to **M6**) are formed by N-type MOSFETs.

[0050] The first electrode of the first transistor (**M1**) is connected to the first power supply (ELVDD) via the fourth transistor (**M4**), and the second electrode of the first transistor (**M1**) is connected to the organic light emitting diode (OLED) via the fifth transistor (**M5**). Also, the gate electrode of the first transistor (**M1**) is connected to the storage capacitor ( $C_{st}$ ). Such a first transistor (**M1**) supplies an

electric current, corresponding to the voltage charged in the storage capacitor (Cst), to the organic light emitting diode (OLED).

[0051] The first electrode of the third transistor (M3) is connected to the first electrode of the first transistor (M1), and the second electrode of the third transistor (M3) is connected to the gate electrode of the first transistor (M1). Also, the gate electrode of the third transistor (M3) is connected to the  $n^{th}$  scan line (Sn). Such a third transistor (M3) is turned on when the scan signals are supplied to the  $n^{th}$  scan line (Sn), to thereby connect the first transistor (M1) in a diode mode. That is, the first transistor (M1) is connected in a diode mode when the third transistor (M3) is turned on.

[0052] The first electrode of the second transistor (M2) is connected to the data line (D), and the second electrode of the second transistor (M2) is connected to the second electrode of the first transistor (M1). Also, the gate electrode of the second transistor (M2) is connected to the  $n^{th}$  scan line (Sn). Such a second transistor (M2) is turned on when the scan signals are supplied to the  $n^{th}$  scan line (Sn), to thereby supply the data signals, supplied to the data lines (D), to the second electrode of the first transistor (M1).

[0053] The first electrode of the fourth transistor (M4) is connected to the first power supply (ELVDD), and the second electrode of the fourth transistor (M4) is connected to the first electrode of the first transistor (M1). Also, the gate electrode of the fourth transistor (M4) is connected to the emission control line (En). Such a fourth transistor (M4) is turned on when the emission control signals are not supplied (namely, when low emission control signals are supplied), to thereby electrically connect the first transistor (M1) with the first power supply (ELVDD).

[0054] The first electrode of the fifth transistor (M5) is connected to the first transistor (M1), and the second electrode of the fifth transistor (M5) is connected to the organic light emitting diode (OLED). Also, the gate electrode of the fifth transistor (M5) is connected to the emission control line (En). Such a fifth transistor (M5) is turned on when the emission control signals are not supplied (namely, when low emission control signals are supplied), to thereby electrically connect the organic light emitting diode (OLED) with the first transistor (M1).

[0055] The first electrode of the sixth transistor (M6) is connected to the storage capacitor (Cst) and the gate electrode of the first transistor (M1), and the second electrode of the sixth transistor (M6) is connected to the reset power supply (Vint). Also, the gate electrode of the sixth transistor (M6) is connected to the  $n-1^{st}$  scan line (Sn-1). Such a sixth transistor (M6) is turned on when the scan signals are supplied to the  $n-1^{st}$  scan line (Sn-1), to thereby reset the storage capacitor (Cst) and the gate electrode of the first transistor (M1). For this purpose, the reset power supply (Vint) is set to a lower voltage value than those of the data signals.

[0056] FIG. 6 is a circuit view showing a detailed configuration in which the demultiplexer is combined with the pixel of FIG. 5.

[0057] In operation and referring to FIG. 4 and FIG. 6, scan signals are first supplied to the  $n-1^{st}$  scan line (Sn-1) during the scan period of the one horizontal period (1 H). If the scan signals are supplied to the  $n-1^{st}$  scan line (Sn-1), then the sixth transistor (M6) included in each of the pixels 140R, 140G, 140B is turned on. If the sixth transistor (M6) is

turned on, then the storage capacitor (Cst) and the gate electrode (or gate terminal) of the first transistor (M1) is connected with the reset power supply (Vint). Then, the storage capacitor (Cst) and the gate electrode of the first transistor (M1) are reset to the voltage of the reset power supply (Vint).

[0058] Subsequently, the first switching element (T1), the second switching element (T2), and the third switching element (T3) are sequentially turned on by the first control signal (CS1) to the third control signal (CS3) sequentially supplied during the data period. If the first switching element (T1) is turned on, then a voltage corresponding to the data signals is charged in the first data capacitor (CdataR) formed in (or on) the first data line (D1). If the second switching element (T2) is turned on, then a voltage corresponding to the data signals is charged in the second data capacitor (CdataG) formed in (or on) the second data line (D2). If the third switching element (T3) is turned on, then a voltage corresponding to the data signals is charged in the third data capacitor (CdataB) formed in (or on) the third data line (D3). At this time, the data signals are not supplied to the pixels 140R, 140G, 140B since the second transistor (M2) included in each of the pixels 140R, 140G, 140B is not set to a turned-on state.

[0059] Subsequently, scan signals are supplied to the  $n^{th}$  scan line (Sn) during the scan period after the data period. If the scan signals are supplied to the  $n^{th}$  scan line (Sn), then the second transistor (M2) and third transistor (M3) included in each of the pixels 140R, 140G, 140B are turned on. If the second transistor (M2) and third transistor (M3) included in each of the pixels 140R, 140G, 140B are turned on, then a voltage corresponding to the data signals, stored in the first data capacitor (CdataR) to the third data capacitor (CdataB), is supplied to the pixels 140R, 140G, 140B.

[0060] Here, the first transistor (M1) is turned on since the voltage of the gate electrode of the first transistor (M1) included in the pixels 140R, 140G, 140B is reset by the reset power supply (Vint) (namely, since the gate electrode of the first transistor (M1) is set to a lower voltage than those of the data signals). If the first transistor (M1) is turned on, then the data signals are supplied to one terminal of the storage capacitor (Cst) via the first transistor (M1) and the third transistor (M3). At this time, a voltage corresponding to the data signals is charged in the storage capacitor (Cst) included in each of the pixels 140R, 140G, 140B.

[0061] Here, in addition to the voltage corresponding to the data signals, a voltage corresponding to a threshold voltage of the first transistor (M1) is further charged in the storage capacitor (Cst). Subsequently, the fourth and fifth transistors (M4, M5) are turned on when the emission control signals are not supplied to the emission control signals (E) (namely, when low emission control signals are supplied to the emission control signals (E)), and therefore an electric current corresponding to the voltage charged in the storage capacitor (Cst) is applied to the organic light emitting diodes (OLED (R), OLED (G), OLED (B)), to thereby generate red, green, and blue lights having a certain (or predetermined) luminance.

[0062] That is, the present invention has an advantage in that the data signals supplied to one output line (O) are supplied to the number i of the data lines (D) using the demultiplexer 162. However, a sufficient charging time may not be ensured since the data signals are supplied to the storage capacitor (Cst) only during the scan period of the one

horizontal period (1H) in the driving method according to the first embodiment of the present invention as shown in FIG. 4. In actuality, the present embodiment ensures a sufficient period when the control signals (CS) are supplied to ensure that a sufficient voltage is charged in the data capacitors (Cdata) during the data period. However, this may still result in shortening the charging time since the scan period may have to be shorter to ensure the sufficient period when the control signals (CS) are supplied.

[0063] FIG. 7 is a waveform view showing a method for driving an organic light emitting display device according to a second embodiment of the present invention.

[0064] Referring to FIG. 7, in the method for driving this organic light emitting display device according to the second embodiment of the present invention, the scan driver 110 sequentially supplies scan signals during each horizontal period (1H). Also, the scan driver 110 supplies emission control signals so that the scan driver 110 can be overlapped with two scan signals.

[0065] The demultiplexer control unit 170 supplies the first control signal (CS1), the second control signal (CS2), and the third control signal (CS3) so that the demultiplexer control unit 170 can be overlapped with the scan signals during each horizontal period (1H). Here, the first control signal (CS1), the second control signal (CS2), and the third control signal (CS3) are sequentially supplied so that the first control signal (CS1), the second control signal (CS2), and the third control signal (CS3) are not overlapped with each other.

[0066] The data driver 120 sequentially supplies the number i of the data signals (R, G, B) to each of the output lines (O) during a period when the scan signals are supplied. Here, the data driver 120 supplies the reset voltage (Vr) among the data signals (R, G, B).

[0067] In more detail, the data driver 120 supplies the data signals (R, G, B) so that the data driver 120 can be overlapped with the control signals (CS1, CS2, CS3) when the control signals (CS1, CS2, CS3) are supplied. For example, the data driver 120 supplies the red data signal (R) so that the data driver 120 can be overlapped with the first control signal (CS1), and supplies the green data signal (G) so that the data driver 120 can be overlapped with the second control signal (CS2). Also, the data driver 120 supplies the blue data signal (B) so that the data driver 120 can be overlapped with the third control signal (CS3).

[0068] Also, the data driver 120 supplies the reset voltage (Vr) to the output lines (O) after each of the data signals (R, G, B) is supplied to the output lines (O). For example, the data driver 120 supplies the reset voltage (Vr) to the output lines (O) after the supply of the red data signals (R) is interrupted. Here, the reset voltage (Vr) is partially overlapped with the first control signal (CS1), and is continued to be supplied until the second control signal (CS2) is supplied. Also, the data driver 120 supplies the reset voltage (Vr) to the output lines (O) after the supply of the green data signals (G) is interrupted. Here, the reset voltage (Vr) is partially overlapped with the second control signal (CS2), and is continued to be supplied until the third control signal (CS3) is supplied. Also, the data driver 120 supplies the reset voltage (Vr) to the output lines (O) after the supply of the blue data signals (B) is interrupted.

[0069] Here, the reset voltage (Vr) is partially overlapped with the third control signal (CS3), and is continued to be supplied until the next first control signal (CS1) is supplied.

Such a reset voltage (Vr) is used for resetting the voltage charged in the data capacitor (Cdata) (namely, a parasitic capacitor) included in each of the data lines (D). For this purpose, the reset voltage (Vr) is set to a lower voltage value than those of the data signals. That is, the reset voltage (Vr) is set to a lower voltage value than that of the lowest data signal that may be supplied to the data driver 120. For example, the reset voltage (Vr) may be set to the same voltage value as that of the reset power supply (Vint).

[0070] In operation and referring to FIG. 6 and FIG. 7, the pixels 140 connected to the n-1<sup>st</sup> scan line (Sn-1) and the n<sup>th</sup> scan line (Sn) are shown in FIG. 6.

[0071] In FIG. 6 and 7, scan signals are first supplied to the n-1<sup>st</sup> scan line (Sn-1). If the scan signals are supplied to the n-1<sup>st</sup> scan line (Sn-1), then the sixth transistor (M6) included in each of the pixels 140R,140G,140B is turned on. If the sixth transistor (M6) is turned on, then one terminal of the storage capacitor (Cst) and the gate electrode of the first transistor (M1) are reset to have a voltage of the reset power supply (Vint).

[0072] In addition, the first control signal (CS1) to the third control signal (CS3) are sequentially supplied during a period when the scan signals are supplied to the n-1<sup>st</sup> scan line (Sn-1). Then, the first switching element (T1) to the third switching element (T3) are sequentially turned on, and simultaneously the data signals are supplied to the data lines (D1 to D3). In this case, the data signals are not supplied to the pixels 140R,140G,140B connected to the n<sup>th</sup> scan line (Sn) since the scan signals are not supplied to the n<sup>th</sup> scan line (Sn), that is, since the second transistor (M2) is turned off.

[0073] Subsequently, the scan signals are supplied to the n<sup>th</sup> scan line (Sn) during the next horizontal period. If the scan signals are supplied to the n<sup>th</sup> scan line (Sn), then the second transistor (M2) and the third transistor (M3) included in each of the pixels 140R,140G,140B are turned on. Also, the first switching element (T1), the second switching element (T2), and the third switching element (T3) are sequentially turned on by the first control signal (CS1) to the third control signal (CS3) during a period when the scan signals are supplied to the n<sup>th</sup> scan line (Sn).

[0074] If the first switching element (T1) is turned on, then the red data signal (R) supplied to the first output line (O1) is supplied to the first data line (D1). The red data signal (R) supplied to the first data line (D1) is supplied to the pixel 140R via the second transistor (M2) of the red pixel 140R. In this case, the first transistor (M1) of the red pixel 140R is turned on since the gate electrode of the first transistor (M1) in the red pixel 140R is reset by the reset power supply (Vint). If the first transistor (M1) of the red pixel 140R is turned on, then the red data signal (R) is supplied to one terminal of the storage capacitor (Cst) via the first transistor (M1) and the third transistor (M3) of the red pixel 140R. At this time, voltages corresponding to the data signal and the threshold voltage of the first transistor (M1) are charged in the storage capacitor (Cst).

[0075] Subsequently, the reset voltage (Vr) is supplied to the first output line (O1) so that the reset voltage (Vr) can be overlapped with the first control signal (CS1) during some period. The reset voltage (Vr) supplied to the first output line (O1) changes a voltage of the parasitic capacitor (CdataR) (namely, the first data capacitor) of the first data line (D1) into a voltage of the reset voltage (Vr). In addition, although the parasitic capacitor (CdataR) of the first data line (D1) is

changed to have the voltage of the reset voltage ( $V_r$ ), a voltage charged in the red pixel **140R** is maintained stably. That is, the voltage charged in the storage capacitor ( $C_{st}$ ) is not supplied to the first data line ( $D_1$ ) again but maintained stably since the first transistor ( $M_1$ ) is connected in a diode mode.

[0076] If the second switching elements are turned on by the second control signal ( $CS_2$ ), then the green data signal ( $G$ ) supplied to the first output line ( $O_1$ ) is supplied to the second data line ( $D_2$ ). The green data signal ( $G$ ) supplied to the second data line ( $D_2$ ) is supplied to the green pixel **140G** via the second transistor ( $M_2$ ) of the green pixel **140G**. In this case, the first transistor ( $M_1$ ) of the green pixel **140G** is turned on since the gate electrode of the first transistor ( $M_1$ ) in the green pixel **140G** is reset by the reset power supply ( $V_{int}$ ). If the first transistor ( $M_1$ ) of the green pixel **140G** is turned on, then the green data signal ( $G$ ) is supplied to one terminal of the storage capacitor ( $C_{st}$ ) via the first transistor ( $M_1$ ) and the third transistor ( $M_3$ ) of the green pixel **140G**. At this time, voltages corresponding to the data signals and the threshold voltage of the first transistor ( $M_1$ ) are charged in the storage capacitor ( $C_{st}$ ).

[0077] Subsequently, the reset voltage ( $V_r$ ) is supplied to the first output line ( $O_1$ ) so that the reset voltage ( $V_r$ ) can be overlapped with the second control signal ( $CS_2$ ) during some period. The reset voltage ( $V_r$ ) supplied to the first output line ( $O_1$ ) changes a voltage of the parasitic capacitor ( $C_{dataG}$ ) (namely, the second data capacitor) of the second data line ( $D_2$ ) into a voltage of the reset voltage ( $V_r$ ). In addition, although the parasitic capacitor ( $C_{dataG}$ ) of the second data line ( $D_2$ ) is changed to have the voltage of the reset voltage ( $V_r$ ), a voltage charged in the green pixel **140G** is maintained stably. That is, the voltage charged in the storage capacitor ( $C_{st}$ ) is not supplied to the second data line ( $D_2$ ) again but maintained stably since the first transistor ( $M_1$ ) is connected in a diode mode.

[0078] If the third switching element ( $T_3$ ) is turned on by the third control signal ( $CS_3$ ), then the blue data signal ( $B$ ) supplied to the first output line ( $O_1$ ) is supplied to the third data line ( $D_3$ ). The blue data signal ( $B$ ) supplied to the third data line ( $D_3$ ) is supplied to the blue pixel **140B** via the second transistor ( $M_2$ ) of the blue pixel **140B**. In this case, the first transistor ( $M_1$ ) of the blue pixel **140B** is turned on since the gate electrode of the first transistor ( $M_1$ ) in the blue pixel **140B** is reset by the reset power supply ( $V_{int}$ ). If the first transistor ( $M_1$ ) of the blue pixel **140B** is turned on, then the blue data signal ( $B$ ) is supplied to one terminal of the storage capacitor ( $C_{st}$ ) via the first transistor ( $M_1$ ) and the third transistor ( $M_3$ ) of the blue pixel **140B**. At this time, voltages corresponding to the data signals and the threshold voltage of the first transistor ( $M_1$ ) are charged in the storage capacitor ( $C_{st}$ ).

[0079] Subsequently, the reset voltage ( $V_r$ ) is supplied to the first output line ( $O_1$ ) so that the reset voltage ( $V_r$ ) can be overlapped with the third control signal ( $CS_3$ ) during some period. The reset voltage ( $V_r$ ) supplied to the first output line ( $O_1$ ) changes a voltage of the parasitic capacitor ( $C_{dataB}$ ) (namely, the third data capacitor) of the third data line ( $D_3$ ) into a voltage of the reset voltage ( $V_r$ ). In addition, although the parasitic capacitor ( $C_{dataB}$ ) of the third data line ( $D_3$ ) is changed to have the voltage of the reset voltage ( $V_r$ ), a voltage charged in the blue pixel **140B** is maintained stably. That is, the voltage charged in the storage capacitor ( $C_{st}$ ) is

not supplied to the second data line ( $D_2$ ) again but maintained stably since the first transistor ( $M_1$ ) is connected in a diode mode.

[0080] As described above, the driving method according to the second embodiment of the present invention has an advantage in that the manufacturing cost may be lowered since the data signals supplied to one output line ( $O$ ) may be supplied to the number  $i$  of the data lines ( $D$ ). Also, in the present embodiment, the scan signals are supplied during one horizontal period and the control signals ( $CS_1$ ,  $CS_2$ ,  $CS_3$ ) are sequentially supplied during a period when the scan signals are supplied. Also, a charging time of the data signals may be improved by supplying the desired data signals during a period when the control signals are supplied, and therefore a sufficient charging time of the pixels **140** may be ensured.

[0081] In the present embodiment, the reset voltage ( $V_r$ ) supplied to the output lines ( $O$ ) may allow the pixels to be driven stably. For this detailed description, the second transistor ( $M_2$ ) included in each of the pixels **140R**, **140G**, **140B** is turned on during a period when the scan signals are supplied. Here, if the data lines ( $D_1$  to  $D_3$ ) are not reset by the reset voltage ( $V_r$ ), then pixel voltages of the green pixel **140G** and the blue pixel **140B** are changed during a period when the first switching element ( $T_1$ ) is turned on since the first control signal ( $CS_1$ ) is supplied to the green pixel **140G** and the blue pixel **140B**. That is, a voltage of the previous data signal, which is charged in the third data capacitor ( $C_{dataB}$ ) via the second transistor ( $M_2$ ) of the blue pixel **140B**, is supplied to the blue pixel **140B** during a period when the first control signal ( $CS_1$ ) is supplied. As a result, the pixels are not driven stably since the voltage reset by the reset power supply ( $V_{int}$ ) is changed into the voltage of the previous data signal. For example, although the third control signal ( $CS_3$ ) is supplied to turn on the third switching element ( $T_3$ ), a voltage of the blue pixel **140B** may be undesirably maintained at a voltage level of the previous data signal.

[0082] Accordingly, a desired voltage may be allowed to be charged in the pixels **140** by supplying the reset voltage (or signal) ( $V_r$ ) so that the reset signal ( $V_r$ ) can be overlapped with control signals ( $CS_1$ ,  $CS_2$ ,  $CS_3$ ) during some period in the present invention. However, since the pixels **140** are additionally connected to wires connected to the reset power supply ( $V_{int}$ ), the structure of the pixels **140** of the present embodiment as shown in FIG. 5 has an additional complexity. To reduce the complexity, another pixel adapted to be driven by the method according to the second embodiment of the present invention is shown in FIG. 8.

[0083] FIG. 8 is a circuit view showing the another pixel adapted to be driven by the method according to the second embodiment of the present invention. For convenience of description, pixels connected to the  $n-1^{st}$  scan line ( $S_{n-1}$ ) and the  $n^{th}$  scan line ( $S_n$ ) are shown in FIG. 8.

[0084] Referring to FIG. 8, the pixels **140** include an organic light emitting diode (OLED), and a pixel circuit **142'** connected to the data line ( $D$ ), the scan lines ( $S_{n-1}$ ,  $S_n$ ), and the emission control line ( $E_n$ ) to control the organic light emitting diode (OLED).

[0085] An anode electrode of the organic light emitting diode (OLED) is connected to the pixel circuit **142'**, and a cathode electrode is connected to a second power supply (ELVSS). The second power supply (ELVSS) is set to a lower voltage, for example, ground voltage, than that of the

first power supply (ELVDD). The organic light emitting diode (OLED) generates light of red, green, or blue color to correspond to a current capacity supplied from the pixel circuit 142'.

[0086] The pixel circuit 142' includes a first transistor (M1), a second transistor (M2), a third transistor (M3), a fourth transistor (M4), a fifth transistor (M5), a sixth transistor (M6), and a storage capacitor (Cst). Here, the first to sixth transistors (M1 to M6) are shown as P-type MOSFETs in FIG. 8, but the present invention is not limited thereto.

[0087] Here, the first electrode of the first transistor (M1) is connected to the first power supply (ELVDD) via the fourth transistor (M4), and the second electrode of the first transistor (M1) is connected to the organic light emitting diode (OLED) via the fifth transistor (M5). Also, the gate electrode of the first transistor (M1) is connected to one terminal of the storage capacitor (Cst). Such a first transistor (M1) supplies an electric current corresponding to the voltage, charged in the storage capacitor (Cst), to the organic light emitting diode (OLED).

[0088] The first electrode of the third transistor (M3) is connected to the first electrode of the first transistor (M1), and the second electrode of the third transistor (M3) is connected to the gate electrode of the first transistor (M1). Also, the gate electrode of the third transistor (M3) is connected to the n<sup>th</sup> scan line (Sn). Such a third transistor (M3) is turned on when the scan signals are supplied to the n<sup>th</sup> scan line (Sn), to thereby connect the first transistor (M1) in a diode mode.

[0089] The first electrode of the second transistor (M2) is connected to the data lines (D), and the second electrode of the second transistor (M2) is connected to the second electrode of the first transistor (M1). Also, the gate electrode of the second transistor (M2) is connected to the n<sup>th</sup> scan line (Sn). Such a second transistor (M2) is turned on when the scan signals are supplied to the n<sup>th</sup> scan line (Sn), to thereby supply the data signals, supplied to the data lines (D), to the second electrode of the first transistor (M1).

[0090] The first electrode of the fourth transistor (M4) is connected to the first power supply (ELVDD), and the second electrode of the fourth transistor (M4) is connected to the first electrode of the first transistor (M1). Also, the gate electrode of the fourth transistor (M4) is connected to the emission control line (En). Such a fourth transistor (M4) is turned on when the emission control signals are not supplied, to thereby electrically connect the first transistor (M1) with the first power supply (ELVDD).

[0091] The first electrode of the fifth transistor (M5) is connected to the second electrode of the first transistor (M1), and the second electrode of the fifth transistor (M5) is connected to the organic light emitting diode (OLED). Also, the gate electrode of the fifth transistor (M5) is connected to the emission control line (En). Such a fifth transistor (M5) is turned on when the emission control signals are not supplied, to thereby electrically connect the organic light emitting diode (OLED) with the first transistor (M1).

[0092] The first electrode of the sixth transistor (M6) is connected to the gate electrode of the first transistor (M1), and the second electrode of the sixth transistor (M6) is connected to the data line (D). Also, the gate electrode of the sixth transistor (M6) is connected to the n-1<sup>st</sup> scan line (Sn-1). Such a sixth transistor (M6) is turned on when the

scan signals are supplied to the n-1<sup>st</sup> scan line (Sn-1), to thereby reset the gate electrode of the first transistor (M1) to the reset voltage (Vr).

[0093] FIG. 9 is a circuit view showing a configuration in which the demultiplexer is combined with the pixel of FIG. 8. Pixels connected to the n-1<sup>st</sup> scan line (Sn-1) and the n<sup>th</sup> scan line (Sn) are shown in FIG. 9.

[0094] In operation and referring to FIG. 7 and FIG. 9, scan signals are first supplied to the n-1<sup>st</sup> scan line (Sn-1) (the previous scan line), and simultaneously emission control signals are supplied to the n<sup>th</sup> emission control line (En). If the scan signals are supplied to the n-1<sup>st</sup> scan line (Sn-1), then the sixth transistor (M6) included in each of the pixels 140R, 140G, 140B is turned on. Also, if the emission control signals are supplied to the n<sup>th</sup> emission control line (En), then the fourth transistor (M4) and the fifth transistor (M5) are turned off.

[0095] In addition, the first control signal (CS1), the second control signal (CS2), and the third control signal (CS3) are sequentially supplied during a period when the scan signals are supplied to the n-1<sup>st</sup> scan line (Sn-1). If the first control signal (CS1) is supplied to the first switching element (T1), then the first switching element (T1) is turned on to sequentially supply the red data signal (R) and the reset voltage (Vr). At this time, the gate electrode of the first transistor (M1) and the one terminal of the storage capacitor (Cst) are reset to the reset voltage (Vr) since the sixth transistor (M6) included in the red pixel 140R is set to a turned-on state. That is, the gate electrode of the first transistor (M1) and the one terminal of the storage capacitor (Cst), which are all included in the red pixel 140R, are changed to have the reset voltage (Vr) by the reset voltage (Vr) supplied after the red data signal (R).

[0096] In the same manner, a gate electrode of the first transistor (M1) and one terminal of the storage capacitor (Cst), which are all included in the green pixel 140G, are reset to the reset voltage (Vr) when the second control signal (CS2) is supplied. Also, a gate electrode of the first transistor (M1) and one terminal of the storage capacitor (Cst), which are all included in the blue pixel 140B, are reset to the reset voltage (Vr) when the third control signal (CS3) is supplied.

[0097] Subsequently, the scan signals are supplied to the n<sup>th</sup> scan line (Sn) (a current scan line). If the scan signals are supplied to the n<sup>th</sup> scan line (Sn), then the second transistor (M2) and the third transistor (M3) included in each of the pixels 140R, 140G, 140B are turned on. Also, the first switching element (T1), the second switching element (T2), and the third switching element (T3) are sequentially turned on by the first control signal (CS1) to the third control signal (CS3) during a period when the scan signals are supplied to the n<sup>th</sup> scan line (Sn).

[0098] If the first switching element (T1) is turned on, then the red data signal (R) supplied to the first output line (O1) is supplied to the first data line (D1). The red data signal (R) supplied to the first data line (D1) is supplied to the red pixel 140R via the second transistor (M2) of the red pixel 140R. In this case, the first transistor (M1) of the red pixel 140R is turned on since the gate electrode of the first transistor (M1) in the red pixel 140R is reset to the reset voltage (Vr). If the first transistor (M1) of the red pixel 140R is turned on, then the red data signal (R) is supplied to one terminal of the storage capacitor (Cst) via the first transistor (M1) and the third transistor (M3) of the red pixel 140R. At this time,

voltages corresponding to the data signal and the threshold voltage of the first transistor (M1) are charged in the storage capacitor (Cst).

[0099] Subsequently, the reset voltage (Vr) is supplied to the first output line (O1) so that the reset voltage (Vr) can be overlapped with the first control signal (CS1) during some period. The reset voltage (Vr) supplied to the first output line (O1) changes a voltage of the parasitic capacitor (CdataR) of the first data line (D1) into the voltage of the reset voltage (Vr). Also, although the parasitic capacitor (CdataR) of the first data line (D1) is changed to have the voltage of the reset voltage (Vr), a voltage charged in the red pixel 140R is maintained stably. That is, the voltage charged in the storage capacitor (Cst) is not supplied to the first data line (D1) again but maintained stably since the first transistor (M1) is connected in a diode mode.

[0100] If the second switching element (T2) is turned on by the second control signal (CS2), then the green data signal (G) supplied to the first output line (O1) is supplied to the second data line (D2). The green data signal (G) supplied to the second data line (D2) is supplied to the green pixel 140G via the second transistor (M2) of the green pixel 140G. In this case, the first transistor (M1) of the green pixel 140G is turned on since the gate electrode of the first transistor (M1) in the green pixel 140G is reset by the reset voltage (Vr). If the first transistor (M1) of the green pixel 140G is turned on, then the green data signal (G) is supplied to one terminal of the storage capacitor (Cst) via the first transistor (M1) and the third transistor (M3) of the green pixel 140G. At this time, voltages corresponding to the data signals and the threshold voltage of the first transistor (M1) are charged in the storage capacitor (Cst).

[0101] Subsequently, the reset voltage (Vr) is supplied to the first output line (O1) so that reset voltage (Vr) can be overlapped with the second control signal (CS2) during some period. The reset voltage (Vr) supplied to the first output line (O1) changes a voltage of the parasitic capacitor (CdataG) of the second data line (D2) into a voltage of the reset voltage (Vr). Also, although the parasitic capacitor (CdataG) of the second data line (D2) is changed to have the voltage of the reset voltage (Vr), a voltage charged in the green pixel 140G is maintained stably. That is, the voltage charged in the storage capacitor (Cst) is not supplied to the second data line (D2) again but maintained stably since the first transistor (M1) is connected in a diode mode.

[0102] If the third switching element (T3) is turned on by the third control signal (CS3), then the blue data signal (B) supplied to the first output line (O1) is supplied to the third data line (D3). The blue data signal (B) supplied to the third data line (D3) is supplied to the blue pixel 140B via the second transistor (M2) of the blue pixel 140B. In this case, the first transistor (M1) of the blue pixel 140B is turned on since the gate electrode of the first transistor (M1) in the blue pixel 140B is reset by the reset voltage (Vr). If the first transistor (M1) of the blue pixel 140B is turned on, then the blue data signal (B) is supplied to one terminal of the storage capacitor (Cst) via the first transistor (M1) and the third transistor (M3) of the blue pixel 140B. At this time, voltages corresponding to the data signals and the threshold voltage of the first transistor (M1) are charged in the storage capacitor (Cst).

[0103] Subsequently, the reset voltage (Vr) is supplied to the output line (O1) so that the reset voltage (Vr) can be overlapped with the third control signal (CS3) during some

period. The reset voltage (Vr) supplied to the first output line (O1) changes a voltage of the parasitic capacitor (CdataB) of the third data line (D3) to the reset voltage (Vr). Also, although the voltage of the parasitic capacitor (CdataB) of the third data line (D3) is changed to the reset voltage (Vr), the voltage charged in the blue pixel 140B is maintained stably. That is, the voltage charged in the storage capacitor (Cst) is maintained stably without being supplied to the second data line (D2) since the first transistor (M1) is connected in a diode mode.

[0104] As described above, an embodiment of the present invention can lower the manufacturing cost because the data signals supplied to one output line (O1) may be supplied to the number i of the data lines (D). Also, an embodiment of the present invention can increase (or improve) the supplying time of the data signals because the control signals (CS1, CS2, CS3) are supplied during a period when the scan signals are supplied, to thereby ensure a sufficient charging time of the pixels 140. Also, in an embodiment of the present invention, since a pixel can be reset by the reset voltages (Vr) supplied from the data lines (D) according to the second embodiment of the present invention, the reset power lines may be omitted from the pixel, to thereby improve an aperture ratio.

[0105] Also as described above, a pixel according to an embodiment of the present invention, an organic light emitting display device using the same, and a driving method thereof can reduce the manufacturing cost because data signals, supplied to one output line, are supplied to a plurality of data lines. In addition, a pixel according to an embodiment of the present invention, an organic light emitting display device using the same, and a driving method thereof can improve a charging time of the pixel by supplying and overlapping scan signals and control signals with each other because reset voltages are supplied after data signals are supplied. Moreover, a pixel according to an embodiment of the present invention, an organic light emitting display device using the same, and a driving method thereof can accomplish a simple structure of the pixel because the pixel is reset using a reset voltage without additional reset power lines.

[0106] While the invention has been described in connection with certain exemplary embodiments, it will be appreciated by those skilled in the art that the invention is not limited to the disclosed embodiments, but, on the contrary, is intended to cover various modifications included within the principles and spirit of the invention, the scope of which is defined in the claims and their equivalents.

#### What is claimed is:

1. A method for driving an organic light emitting display device, the method comprising:

supplying a data signal and a reset voltage to an output line during a horizontal period;

supplying the data signal and the reset voltage, supplied to the output line, to a plurality of data lines using a demultiplexer;

charging a voltage corresponding to the data signal in a pixel connected with one of the data lines during a period when a scan signal is supplied to a current scan line of the pixel; and

allowing the pixel to emit light corresponding to the charged voltage.

**2.** The method for driving the organic light emitting display device according to claim 1, for each of the data lines, the reset voltage is supplied after the data signal is supplied.

**3.** The method for driving the organic light emitting display device according to claim 2, wherein the data signal comprises a first number of data signals supplied to the output line during the horizontal period and the reset voltage comprises a second number of reset voltages supplied during the horizontal period, and wherein the first number is equal to the second number.

**4.** The method for driving the organic light emitting display device according to claim 1, wherein the pixel is reset by a reset power supply connected to the pixel during a period when the scan signal is supplied to a previous scan line of the pixel, and is charged with the voltage corresponding to the data signal supplied to the pixel by itself during a period when the scan signal is supplied to the current scan line of the pixel.

**5.** The method for driving the organic light emitting display device according to claim 4, wherein the reset power supply is set to a lower voltage level than a voltage of the data signal.

**6.** The method for driving the organic light emitting display device according to claim 1, wherein the pixel is reset by the reset voltage during a period when the scan signal is supplied to a previous scan line of the pixel, and is charged with the voltage corresponding to the data signal supplied to the pixel by itself during a period when the scan signal is supplied to the current scan line of the pixel.

**7.** The method for driving the organic light emitting display device according to claim 6, wherein the reset voltage is set to a lower voltage level than a voltage of the data signal.

**8.** The method for driving the organic light emitting display device according to claim 1, wherein the demultiplexer includes a plurality of switching elements between the output line and the data lines, and the switching elements are sequentially turned on during a period when the scan signal is supplied.

**9.** An organic light emitting display device comprising:

a data driver for supplying a data signal and a reset voltage to an output line during every horizontal period;

a demultiplexer coupled to the output line to supply the data signal and the reset voltage to a plurality of data lines;

a scan driver for supplying a scan signal during every horizontal period; and

a pixel connected with one of the data lines, a previous scan line, and a current scan line,

wherein the pixel is reset by the reset voltage during a period when the scan signal is supplied to the previous scan line, and is charged with a voltage corresponding to the data signal when the scan signal is supplied to the current scan line.

**10.** The organic light emitting display device according to claim 9, wherein for each of the data lines, the demultiplexer supplies the reset voltage after the data signal is supplied.

**11.** The organic light emitting display device according to claim 10, wherein the data signal supplied by the data driver during every horizontal period comprises a first number of data signals and the reset voltage supplied by the data driver

during every horizontal period comprises a second number of reset voltages, and wherein the first number is equal to the second number.

**12.** The organic light emitting display device according to claim 9, wherein the demultiplexer includes a plurality of switching elements arranged between the output line and the data lines.

**13.** The organic light emitting display device according to claim 12, further comprising a demultiplexer control unit for sequentially supplying a plurality of control signals to sequentially turn on the switching elements during a period when the scan signal is supplied.

**14.** The organic light emitting display device according to claim 9, wherein the pixel comprises:

- an organic light emitting diode;

- a storage capacitor for charging a voltage corresponding to the data signal;

- a first transistor for supplying an electric current, corresponding to a voltage stored in the storage capacitor, to the organic light emitting diode;

- a second transistor connected to the one of the data lines, the current scan line, and a second electrode of the first transistor, the second transistor being adapted to turn on when the scan signal is supplied to the current scan line;

- a third transistor connected between a first electrode and a gate electrode of the first transistor and being adapted to turn on when the scan signal is supplied to the current scan line; and

- a fourth transistor connected between the gate electrode of the first transistor and the one of the data lines and being adapted to turn on when the scan signal is supplied to the previous scan line.

**15.** The organic light emitting display device according to claim 14, further comprising:

- a fifth transistor connected between the gate electrode of the first transistor and the storage capacitor; and

- a sixth transistor connected between the second electrode of the first transistor and the organic light emitting diode.

**16.** The organic light emitting display device according to claim 15, wherein the fifth transistor is connected to the gate electrode of the first transistor via the third transistor.

**17.** The organic light emitting display device according to claim 15, wherein the fifth transistor and the sixth transistor are adapted to turn off during a period when an emission control signal is supplied from the scan driver, and adapted to remain turned on during other periods except for the period when the emission control signal is supplied from the scan driver.

**18.** The organic light emitting display device according to claim 16, wherein the emission control signal is supplied and overlapped with the scan signal supplied to the previous scan line and the scan signal supplied to the current scan line.

**19.** A pixel comprising:

- an organic light emitting diode;

- a storage capacitor for charging a voltage corresponding to a data signal supplied to one of a plurality of data lines;

- a first transistor for supplying an electric current, corresponding to a voltage charged in the storage capacitor, to the organic light emitting diode;

a second transistor connected to the one of the data lines, a current scan line, and a second electrode of the first transistor, the second transistor being adapted to turn on when a scan signal is supplied to the current scan line; a third transistor connected between a first electrode and a gate electrode of the first transistor and being adapted to turn on when the scan signal is supplied to the current scan line; and a fourth transistor connected between the gate electrode of the first transistor and the one of the data lines and

being adapted to turn on when the scan signal is supplied to a previous scan line.

**20.** The pixel according to claim **18**, further comprising; a fifth transistor connected between the first electrode of the first transistor and the storage capacitor; and a sixth transistor connected between the second electrode of the first transistor and the organic light emitting diode.

\* \* \* \* \*

|                |                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素，有机发光显示装置及其驱动方法                                                                                              |         |            |

| 公开(公告)号        | <a href="#">US20070242016A1</a>                                                                                | 公开(公告)日 | 2007-10-18 |

| 申请号            | US11/655400                                                                                                    | 申请日     | 2007-01-19 |

| [标]申请(专利权)人(译) | 崔相MOO                                                                                                          |         |            |

| 申请(专利权)人(译)    | 崔相MOO                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 崔相MOO                                                                                                          |         |            |

| [标]发明人         | CHOI SANG MOO                                                                                                  |         |            |

| 发明人            | CHOI, SANG MOO                                                                                                 |         |            |

| IPC分类号         | G09G3/36                                                                                                       |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0465 G09G2300/0819 G09G2320/043 G09G2300/0861 G09G2310/0251<br>G09G2310/0297 G09G2300/0842 |         |            |

| 优先权            | 1020060034616 2006-04-17 KR                                                                                    |         |            |

| 其他公开文献         | US9076382                                                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">USPTO</a>                                                                |         |            |

### 摘要(译)

一种用于驱动有机发光显示装置的方法，其能够减少数据驱动器中的输出线的数量，并且确保足够的驱动时间。用于驱动有机发光显示装置的方法包括在水平周期期间向输出线提供数据信号和复位电压的步骤；使用多路分解器将提供给输出线的数据信号和复位电压提供给多条数据线；在将扫描信号提供给像素的当前扫描线的时段期间，对与数据线之一连接的像素中的数据信号对应的电压充电；并允许像素发出对应于充电电压的光。